## Formation and characterization of silicon/carbon nanotube/silicon heterojunctions by local synthesis and assembly

Takeshi Kawano,<sup>a)</sup> Dane Christensen, Supin Chen, Chung Yeung Cho, and Liwei Lin Department of Mechanical Engineering, University of California at Berkeley, Berkeley, California 94720 and Berkeley Sensor and Actuator Center, University of California at Berkeley, Berkeley, California 94720

(Received 15 March 2006; accepted 4 September 2006; published online 19 October 2006)

This work investigates the formation of silicon/multiwalled carbon nanotube/silicon heterojunctions by *in situ* synthesizing carbon nanotubes between two heavily doped, suspended silicon microstructures that are separated  $5-10 \mu m$  apart using the techniques of localized heating and electric-field-assisted self-assembly. The local electric field has the strength of  $0.2-1 \text{ V}/\mu m$ . Tipand root-grown carbon nanotubes are observed to form two different heterojunction morphologies at the tips as the former stop to grow and the latter continue to grow as the growth tips of carbon nanotubes reach the cold silicon. Experimental measurements of the silicon/carbon nanotube/silicon system show linear current-voltage characteristics indicating Ohmic contact behavior. © 2006 American Institute of Physics. [DOI: 10.1063/1.2364151]

Carbon nanotubes (CNTs) have been extensively studied in recent years for various applications that use the unique electrical and physical properties of CNTs.<sup>1–3</sup> For example, the high surface area-to-volume ratio makes CNTs promising as the foundation to build highly sensitive devices. Recent semiconductor advancements further demonstrate the feasibility of using CNTs to construct nanotransistor and other nanodevices.<sup>4–6</sup> The possibility of combining CNTs with onchip integrated circuits (ICs) opens up various applications of CNTs in devices,<sup>7</sup> including physical and biological sensors.

In order to combine CNT and IC technologies, one desirable approach is to construct the on-chip microelectronics first using readily available foundry services and synthesize or assemble CNTs selectively afterwards. Unfortunately, the CNT synthesis process is typically conducted in a furnace at high temperatures, ranging from 600 to 1200 °C, which can cause damages to the on-chip microelectronics made from standard foundry services. Furthermore, it is difficult to control the deposition locations of CNTs and the assembly process. This work presents techniques on the synthesis and assembly of CNTs and the formation of CNTs and heavily doped silicon heterojunctions as the foundations in integrated IC/CNT systems. The synthesis method starts with a micromachined resistive heater coated with a thin catalyst.<sup>8</sup> A second microstructure can be designated next to the first heating microstructure to guide the growth of CNTs via a local electric field.9-11

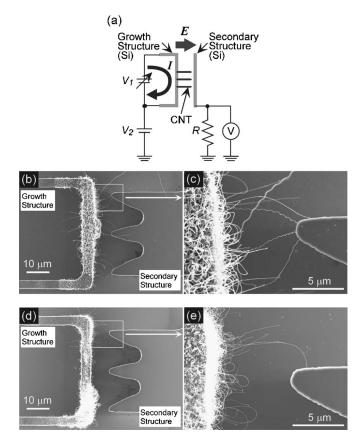

We first prepare suspended silicon microstructures using a silicon-on-insulator (SOI) process.<sup>8</sup> The silicon microstructure is highly doped *p*-type (*p*<sup>+</sup>) single-crystalline silicon, with a resistivity of  $1 \times 10^{-2} \Omega$  cm (impurity concentration of  $1 \times 10^{19}$  cm<sup>-3</sup>). Figure 1(a) shows the schematic diagram of the setup. The typical width and length of the microelectromechanical system (MEMS) microstructures are 5 and 150  $\mu$ m, respectively, and the thickness is 15  $\mu$ m with measured resistance of 380  $\Omega$ . The typical distance between the two suspended microstructure is 5–10  $\mu$ m. A 5-nm-thick Ni–Fe (80%–20% by weight) mixture is evaporated to serve as the catalyst. The synthesis process is accomplished using resistive heating on the growth structure while a local electric field is established between the two silicon microstructures to guide the growth direction of CNTs.<sup>8,11</sup> The circuit

FIG. 1. (a) Schematic diagram of CNT synthesis between silicon microstructures using localized and electric-field-assisted syntheses. The CNTs are synthesized when the growth structure is heated and the local electric field is applied between the silicon microstructures. (b) SEM image of the bridging CNTs with silicon growth structure and silicon secondary structure. (c) Image of the top electrode in the image (b). (d) SEM image of the single CNT with silicon growth structure and silicon secondary structure. (e) Image of the top electrode in the image (d).

89, 163510-1

Downloaded 21 Oct 2006 to 136.152.145.52. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Electronic mail: kawano@me.berkeley.edu

<sup>© 2006</sup> American Institute of Physics

representation in Fig. 1(a) further illustrates the electrical arrangement. A varying bias  $V_1$  is used to resistively heat the growth structure and a dc bias  $V_2$  is applied between the two structures to generate the local electrical field. A resistor, R  $\approx$  18 M $\Omega$ , is connected in series with the secondary structure in order to limit the current flow that could burn the CNTs. A voltmeter V is connected with the secondary structure as an effective technique to monitor the CNT assembly process. Once CNTs are electrically connected with the secondary structure, the voltage V will jump to values higher than  $V_2$ , indicating that CNTs are connected between two microstructures. The synthesis is conducted in a room temperature vacuum chamber of 300 Torr with acetylene  $(C_2H_2)$  gas of 50 SCCM (SCCM denotes cubic centimeter per minute at STP) after the growth structure had been heated to the desired temperature (850–950 °C).<sup>8</sup>

Figure 1(b) shows a scanning electron microscope (SEM) image of self-assembled multiwalled CNTs (MWCNTs) between the two silicon microstructures. The synthesis was done by setting  $V_2$  at 2.5 V and  $V_1$  at 7.5 V. The spacing between the growth structure and the tip of the secondary structure is 8  $\mu$ m. The sharp tip results in an intensified electric filed to enhance the electric-filed directed growth<sup>11</sup> and the estimated electric field at the tip is 1.3 V/ $\mu$ m using finite element simulation. In this test, a total of nine connections are made, as four, two, and three CNTs are visible to make the connections on the top, middle, and bottom electrodes, respectively. Figure 1(c) shows enlarged view SEM image in the region of the top electrode in Fig. 1(b). In a second experiment, only a single CNT is connected as shown in Figs. 1(d) and 1(e). The single CNT connection has been achieved by stopping the heater after the first signal detected on the voltmeter V. It is observed that these CNTs have been able to grow across the two microstructures with the diameter of about 50 nm as characterized under SEM and their growth direction generally follows the electric field gradient near the tip region of the secondary microstructure.

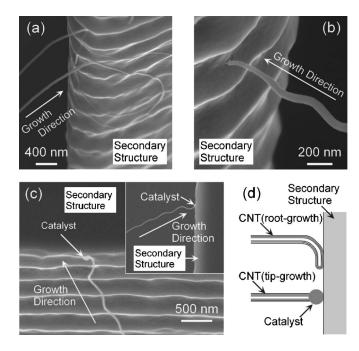

Figure 2 shows several close-up SEM images at the CNT-silicon interface. Two types of CNTs can be synthesized using this local synthesis technique, including the root-growth<sup>12</sup> or tip-growth mechanism.<sup>13</sup> It is observed that the root-grown CNTs can continue to grow after its tip is in contact with the cold secondary structure (at room temperature) as observed in Fig. 2(a) because the root on the growth structure is still hot and the CNT can continue to grow. On the other hand, the tip-grown CNT stops growing once the hot catalyst at its tip is in contact with the cold secondary structure as demonstrated in Fig. 2(b). Figure 2(c) shows another example of a tip-grown CNT in contact with the secondary microstructure where a catalyst can be identified. Figure 2(d) schematically illustrates these two possible interfacial phenomena between CNTs and the secondary silicon microstructure.

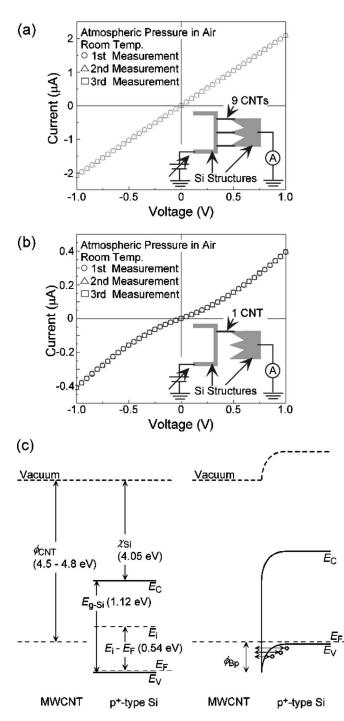

Current *I*-voltage *V* curves in Fig. 3(a) are the results of the sample in Fig. 1(b) and the characteristics are repeatable as demonstrated by the three measurements taken from the same sample. The linear behavior suggests Ohmic contacts of the heterojunctions under a current level of  $10^{-6}$  A and voltage input of ±1 V. The overall resistance of the nine CNTs system is 480 k $\Omega$ . Figure 3(b) shows the *I*-V characteristics of a single CNT connection of Fig. 1(d) and the measured overall resistance is 2.5 M $\Omega$ . The observed linear behavior of these measurements is very different from a pre-

FIG. 2. Interconnection of the CNT and silicon secondary structure. (a) Side-view SEM image showing the interfacial contacts of two CNTs without catalyst at the tips by the root-growth mechanism. (b) Side-view SEM image showing the interfacial contact of a CNT with catalyst at the tip by the tip-growth mechanism. (c) Side-view SEM image shows the interfacial contact of another tip-grown CNT where a catalyst can be defined. Inset; top-view SEM image of the same CNT. (d) Schematic diagram of the interfacial contacts of two types of CNTs, root grown and tip grown, respectively.

vious report on the study of MWCNT and lightly doped *p*-type silicon junction when rectifying behavior was observed.<sup>14</sup>

Energy band diagram is used as illustrated in Fig. 3(c)for the heterojunction between CNT and  $p^+$  silicon. In this diagram,  $\chi_{Si}$  is the electron affinity of silicon (4.05 eV),  $E_{g-Si}$ is the band gap of silicon (1.12 eV), and  $E_F$  is the Fermi level (0.54 eV away from the intrinsic silicon as calculated<sup>15</sup>). Also,  $\phi_{CNT}$  is the work function of the MWCNT (4.5–4.8 eV), where the  $\phi_{CNT}$  covers majority of the MWCNTs, including with and without catalyst at the tip of the CNT.<sup>16,17</sup> For contacts with highly doped silicon, the barrier width becomes narrow and tunneling current will dominate, giving rise to the observed Ohmic behavior.<sup>15</sup> The barrier height is represented as  $\phi_{\rm Bp} = (\chi_{\rm Si} + E_{g-\rm Si}) - \phi_{\rm CNT}$  and calculated as  $0.37 \le \phi_{\rm Bp} \le 0.67$  eV. There are actually two heterojunctions between CNTs and silicon, namely, the one between the CNTs and the growth structure and the one between the CNTs and the secondary structure such that the system is rather complex. The current data we have gathered are insufficient to quantitatively determine individual values of the CNT resistance as well as the contact resistance at these heterojunctions. Analyses are made to investigate these issues. The metal-silicon junction model<sup>15,18</sup> suggests that the specific contact resistivity of the  $MWCNT/p^+$ -silicon contact is  $10^{-5}-10^{-4} \ \Omega \ cm^2$  using a barrier height of 0.4 eV and doping concentration of p-type silicon at 1  $\times 10^{19}$  cm<sup>-3</sup>.<sup>18</sup> The estimated diameter of the CNT is 50 nm (contact area is  $2 \times 10^{-11}$  cm<sup>2</sup> for tip-only contact) and the calculated contact resistance is  $0.5-5 \text{ M}\Omega$  based on the analytical model. This value is in the same order of the measured single CNT resistance at 2.5 M $\Omega$  and further investigations are required to characterize these values.

Downloaded 21 Oct 2006 to 136.152.145.52. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 3. Electrical properties of the MWCNTs. (a) *I*-*V* curves of the bridging nine CNTs. The *I*-*V* curves were measured between the silicon microstructures, and the measurements were carried out three times on the same CNTs shown in Fig. 1(b) (b) *I*-*V* curves of the single CNT. The *I*-*V* curves were measured between the silicon microstructures, and the measurements were carried out three times on the same CNTs shown in Fig. 1(d). These data were taken at room temperature and at atmospheric pressure in air. (c) Energy band diagrams of a MWCNT/*p*<sup>+</sup>-silicon contact. Left image illustrates a MWCNT and *p*<sup>+</sup> silicon before contact. Right image shows the proposed model of MWCNT/*p*<sup>+</sup> silicon after contact at thermal equilibrium.

One important issue is the role of the native oxide at the interface between CNT and silicon secondary structure, as it may become an electrical barrier although the *I-V* curves show no sign of the electrical insulating layer. Analytically,

the thickness of the native oxide is typically 10 Å with a breakdown field of  $3 \times 10^7$  V/cm.<sup>19</sup> As such, the estimated breakdown voltage is 3 V. Considering the voltage applied to the growth structure ( $V_2$  at 2.5 V,  $V_1$  at 7.5 V, total of 10 V) and the fact that synthesis happens in the middle portion of the growth microstructure such that the tip of the grown CNT has a potential with a magnitude around 6.25 V which is higher than the estimated breakdown voltage. Therefore it is expected that breakdown happens on the secondary silicon microstructure and the native oxide is broken during the synthesis.

In summary, we have synthesized and self-assembled MWCNTs between silicon microstructures using localized, selective, and electric-field-assisted techniques. The electrical setup including a voltmeter can monitor the *in situ* electrical responses and identify the instance when CNTs are self-assembled. It is further observed that tip-grown CNTs will stop growing when they reach the secondary silicon microstructure. *I-V* curves of the CNTs show repeatable and linear characteristics indicating that CNT/silicon heterojunction has linear Ohmic behavior, which is explained by the energy band diagram. This synthesis and self-assembly procedure enable bridging CNTs between silicon microstructures for potential use as functional materials with various applications, including sensors and nanoelectronics.

One of the authors (T.K.) is funded by the JSPS Postdoctoral Fellowships for Research Abroad from Japan. This work is supported in part by the NSF Grant No. EEC-0425914.

- <sup>1</sup>T. W. Ebbesen, H. J. Lezec, H. Hiura, J. W. Bennett, H. F. Ghaemi, and T. Thio, Nature (London) **382**, 54 (1996).

- <sup>2</sup>M. M. J. Treacy, T. W. Ebbesen, and J. M. Gibson, Nature (London) **381**, 678 (1996).

- <sup>3</sup>E. Bekyarova, Y. Ni, E. B. Malarkey, V. Montana, J. L. McWilliams, R. C. Haddon, and V. Parpura, J. Biomed. Nano tech. **1**, 3 (2005).

- <sup>4</sup>S. J. Tans, A. R. M. Verschueren, and C. Dekker, Nature (London) **397**, 49 (1998).

- <sup>5</sup>C. Zhou, J. Kong, E. Yenilmez, and H. Dai, Science **290**, 1552 (2000).

- <sup>6</sup>Y. Huang, X. Duan, Y. Cui, L. J. Lauhon, K.-H. Kim, and C. M. Lieber, Science **294**, 1313 (2001).

- <sup>7</sup>Y. Tseng, P. Xuan, A. Javey, R. Malloy, Q. Wang, J. Bokor, and H. Dai, Nano Lett. **4**, 123 (2004).

- <sup>8</sup>O. Englander, D. Christensen, and L. Lin, Appl. Phys. Lett. **82**, 4797 (2003).

- <sup>9</sup>Y. Zhang, A. Chang, J. Cao, Q. Wang, W. Kim, Y. Li, N. Morris, E. Yenilmez, J. Kong, and H. Dai, Appl. Phys. Lett. **79**, 3155 (2001).

- <sup>10</sup>A. Ural, Y. Li, and H. Dai, Appl. Phys. Lett. **81**, 3464 (2002).

- <sup>11</sup>O. Englander, D. Christensen, J. Kim, L. Lin, and S. J. S. Morris, Nano Lett. 5, 705 (2005).

- <sup>12</sup>J. Gavillet, A. Loiseau, C. Journet, F. Willaime, F. Ducastelle, and J.-C. Charlier, Phys. Rev. Lett. 87, 275504 (2001).

- <sup>13</sup>C. Ducati, I. Alexandrou, M. Chhowalla, G. A. J. Amaratunga, and J. Robertson, J. Appl. Phys. **92**, 3299 (2002).

- <sup>14</sup>J. Hu, M. Ouyang, P. Yang, and C. M. Lieber, Nature (London) **399**, 48 (1999).

- <sup>15</sup>S. M. Sze, Semiconductor Devices: Physics and Technology, 2nd ed. (Wiley, New York, 2002), pp. 224–253.

- <sup>16</sup>R. Gao, Z. Pan, and Z. L. Wang, Appl. Phys. Lett. 78, 1757 (2001).

- <sup>17</sup>Z. Xu, X. D. Bai, E. G. Wang, and Z. L. Wang, Appl. Phys. Lett. **87**, 163106 (2005).

- <sup>18</sup>K. K. Ng and R. Liu, IEEE Trans. Electron Devices **37**, 1535 (1990).

- <sup>19</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (Wiley, New York, 1981), pp. 379–407.